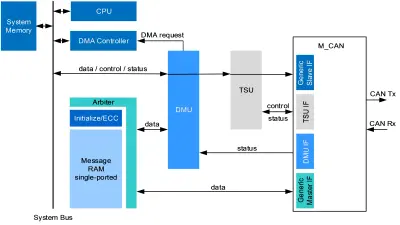

DMU - DMA Unit

Benefits

Offloads tasks from the CPU to the DMA controller

Enables DMA transfers of M_CAN FIFO elements and optional TSU timestamps between Message RAM and system memory.

Available for integration into microcontrollers, ASICs, and FPGAs.

用于ASIC设计的DMA单元

|

DMU

|

|

|

可交付成果

|

|

用于FPGA设计的DMA单元

|

Intel / Altera

|

|

|

AMD / Xilinx

|

|

|

可交付成果

|

|

-

DMU 细节