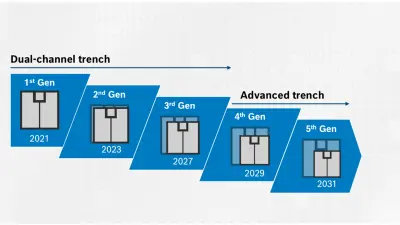

SiC technology roadmap: the journey continues

How generations 3, 4, and 5 of SiC MOSFETs will enable significant performance gains

- Bosch’s parallel, multi-generation development strategy ensures a clearly structured silicon carbide (SiC) technology roadmap with predictable performance leaps and a high level of technological maturity.

- Generations 3, 4, and 5 will feature lower specific on-resistance (RonA), improved switching behavior, and enhanced robustness, while smaller chip sizes unlock clear cost advantages for OEMs.

- Bosch’s trench-based SiC MOSFET technology remains the cornerstone of these advancements, enabling scalability and design flexibility beyond the limits of planar power semiconductor architectures.

Last year, we took you on a journey through the development history of SiC MOSFETs at Bosch. This journey is far from over. From the very beginning, the roadmap has followed a clear goal: to make silicon carbide technology viable across the full range of vehicle classes and thus a key driver of electrified mobility at scale.

The future of SiC technology

Now, we invite you to take a glimpse into the future. With the next stages of the journey ahead, Bosch continues to advance its proven vertical trench technology for SiC MOSFETs, moving step by step towards generations 3, 4, and 5. Ever smaller chip sizes at constant power levels combined with increasing robustness translate into clear cost and scalability benefits. They will pave the way for SiC to move from high-performance applications into the broader electric vehicle market.

But how are such rapid and reliable innovation cycles possible? And how can Bosch already know what gen 5 will look like?

Generation 4 SiC MOSFETs: ultra-narrow pitch design based on trench technology

Building on Gen 3, gen 4 will introduce a major scaling step by significantly reducing the cell pitch. This is where trench technology shows its true potential. Compared to planar architectures, which are inherently limited by surface-based gate and channel geometries, trench technology is a prerequisite for ultra-narrow pitch designs.

The improvements of Gen 4 at a glance:

- By increasing the depth of the trench and reducing its width, the entire cell pitch shrinks from about 3 µm to well below 2 µm, enabling a new level of vertical scaling.

- Gen 4 further increases power density and reduces specific on-resistance while maintaining robustness.

- These gains are achieved using the established trench power MOSFET architecture, without the need for a fundamentally new device concept.

Generation 4 is designed exclusively for 200 mm wafer production and is expected to enter the market around 2029.

Generation 5 SiC MOSFETs: superjunction architecture for the next performance leap

Gen 5 will represent a further milestone with the introduction of superjunction technology into Bosch’s SiC chips while maintaining the advancements of previous generations.

The improvements of Gen 5 at a glance:

- Superjunction allows the drift region resistance to be pushed beyond the conventional unipolar silicon carbide material limit by introducing precisely controlled, alternating p- and n-doped regions.

- This unlocks further reductions in specific on-resistance.

- At the same time, the superjunction concept facilitates a more favorable electric field distribution in the drift region, supporting stable high-voltage operation.

Gen 5 comes with a more complex design and production process. Current development efforts are focusing on suitable manufacturing methods and power module architectures, including measures to mitigate phenomena such as self-excited oscillations at very high switching speeds. Based on today’s development progress, the Bosch experts expect gen 5 SiC MOSFETs to be ready by around 2031. It will represent the next major destination on Bosch’s SiC journey, opening the door to an entirely new performance class.

Increasing power density across successive SiC generations enables more compact system designs and results in improved cost efficiency for automotive OEMs.

Transition to 200 mm wafers: a key enabler for future generations

Since 2024, Bosch has been transitioning silicon carbide wafer production from 150 mm to 200 mm wafers, effectively doubling the usable wafer area. Generation 3 already benefits from the 200 mm platform, with all subsequent generations fully designed for 200 mm manufacturing starting in 2027. This shift lays the industrial foundation for advanced SiC technologies by ensuring greater manufacturing precision and uniformity – both of which are essential for increasingly sophisticated semiconductor designs.

5 Good Reasons for SiC MOSFETs from Bosch:

- Stepwise performance gains across upcoming SiC generations: A clearly defined roadmap delivers measurable improvements in efficiency, power density, MOSFET switching performance, and reliability.

- Smaller chips with system-level cost advantages: Reduced die size at constant power levels enables more compact, cost-efficient inverter and power module designs.

- Robust, system-friendly device behavior: Enhanced short-circuit capability, stable switching characteristics, and reduced parasitic effects simplify system design and increase design margins.

- Scalable manufacturing on 200 mm wafers: Adopting 200 mm SiC wafer technology early on allows for more consistent and reliable manufacturing processes paving the way for advanced technologies.

- Future-ready device architecture: A trench-based SiC platform with a clear path toward superjunction concepts prepares OEMs for the next performance class of SiC power devices.

With its clearly structured SiC technology roadmap, Bosch is guiding SiC technology on its journey toward broad adoption, combining efficiency, power density, robustness, and scalability with increasing cost effectiveness. By advancing trench-based SiC technology, transitioning early to 200 mm wafers, and preparing the path toward superjunction architectures, Bosch delivers high-performing SiC solutions that are industrially mature and ready for large-scale electrification.

Expert perspective:

Jens Baringhaus

Chief Expert for Wideband Gap Technology

Responsible for Bosch's SiC technology roadmap

With deep expertise in semiconductor physics and power electronics, Jens Baringhaus leads the strategic development of future SiC generations at Bosch, determining which technologies advance to the next generation and how they can be combined to deliver both performance and reliability for automotive applications.

Want to learn more about the expert behind Bosch's SiC roadmap? Discover how Jens Baringhaus and his team are shaping the future of power semiconductors and what drives innovation in wideband gap technology.